TP 1

1.Kondisi[kembali]

Percobaan 1 Kondisi 2

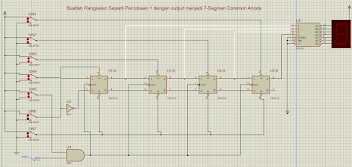

Buatlah Rangkaian Seperti Percobaan 1 dengan output menjadi 7-Segmen Common Anoda

2. Rangkaian Simulasi[kembali]

Gambar Rangkaian :

3. Video Simulasi[kembali]

4. Prinsip Kerja[kembali]

Rangkaian ini berfungsi sebagai pencacah biner 4-bit dengan output berupa angka desimal yang ditampilkan pada 7-segment common anode. Saklar (SW1-SW7) memberikan input logika untuk mengendalikan operasi flip-flop JK (74LS112), yang bekerja berdasarkan sinyal clock dan kombinasi input J serta K untuk menghasilkan kondisi toggle pada setiap pulsa clock. Flip-flop dirangkai secara berurutan sehingga membentuk ripple counter, di mana output dari setiap flip-flop (Q) menjadi input clock untuk flip-flop berikutnya, menghasilkan output biner 4-bit. Output ini kemudian diolah oleh IC driver 7-segment (74LS47), yang mengonversinya menjadi sinyal pengendali untuk menyalakan segmen-segmen pada 7-segment display sesuai dengan angka desimal yang merepresentasikan nilai biner tersebut. Gerbang logika NOT dan AND digunakan untuk membalik dan menggabungkan sinyal guna mengontrol kondisi clock pada flip-flop pertama, memastikan operasi pencacahan yang konsisten.

Sinyal clock ke flip-flop pertama dihasilkan dari kombinasi saklar dan logika AND/NOT.

Output flip-flop pertama (Q) digunakan sebagai input clock ke flip-flop berikutnya, menciptakan efek pencacah berurutan (ripple counter).

J-K Flip Flop

5. Link Download[kembali]

simulasi rangkaian klik disini

Video Simulasi klik disini

Datasheet Seven Segment Klik Disini

Datasheet IC 74LS90 klik disini

Datasheet IC 74LS47 klik disini

Datasheet IC 7493 klik disini

Datasheet Logicprobe klik disini

Datasheet LED klik disini

Video Simulasi klik disini

Datasheet Seven Segment Klik Disini

Datasheet IC 74LS90 klik disini

Datasheet IC 74LS47 klik disini

Datasheet IC 7493 klik disini

Datasheet Logicprobe klik disini

Datasheet LED klik disini

Datasheet AND 4073 klik disini

Komentar

Posting Komentar